Programming the 65816 Including the 6502, 65C02, and 65802 (1986)

Part V. Reference

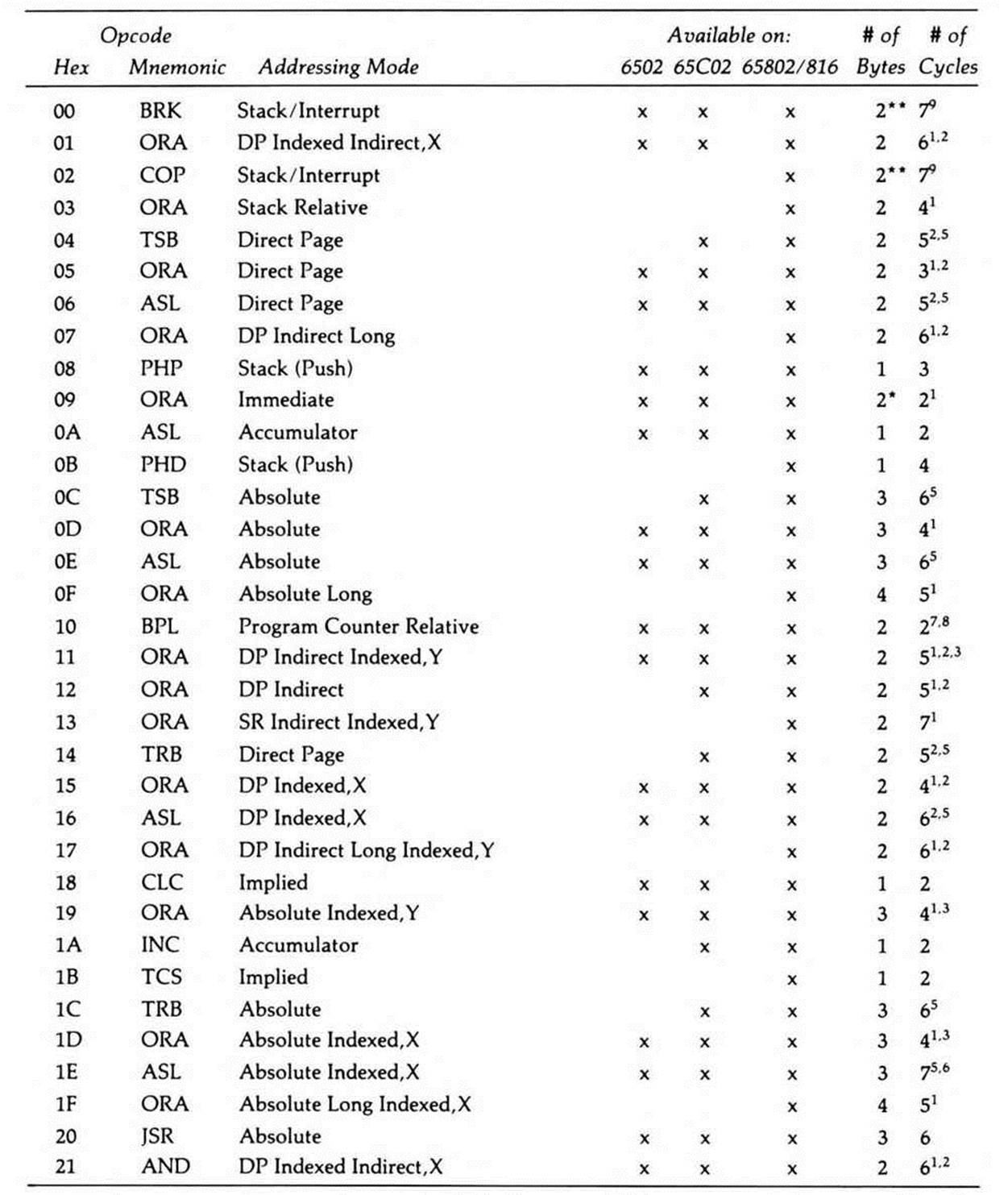

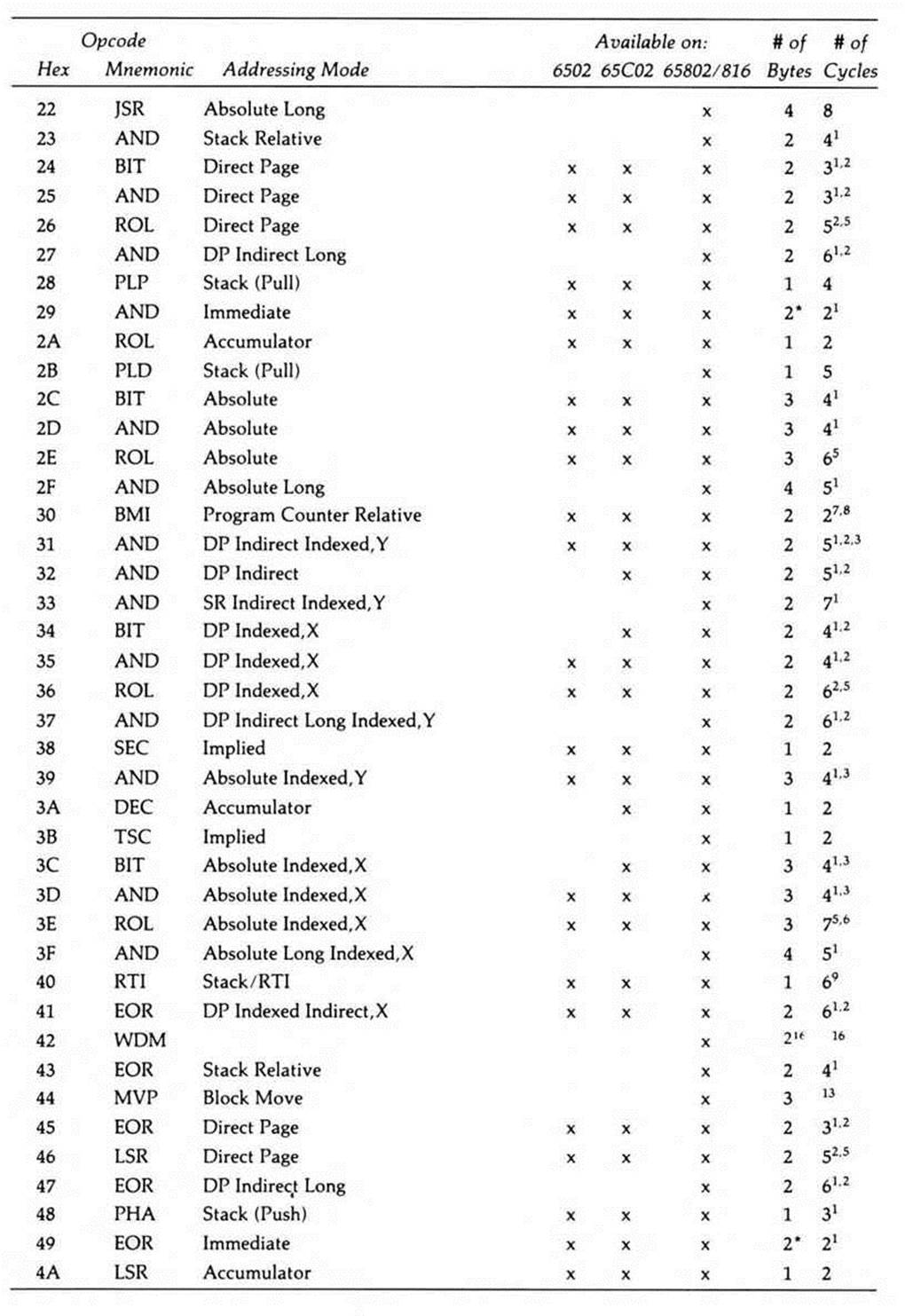

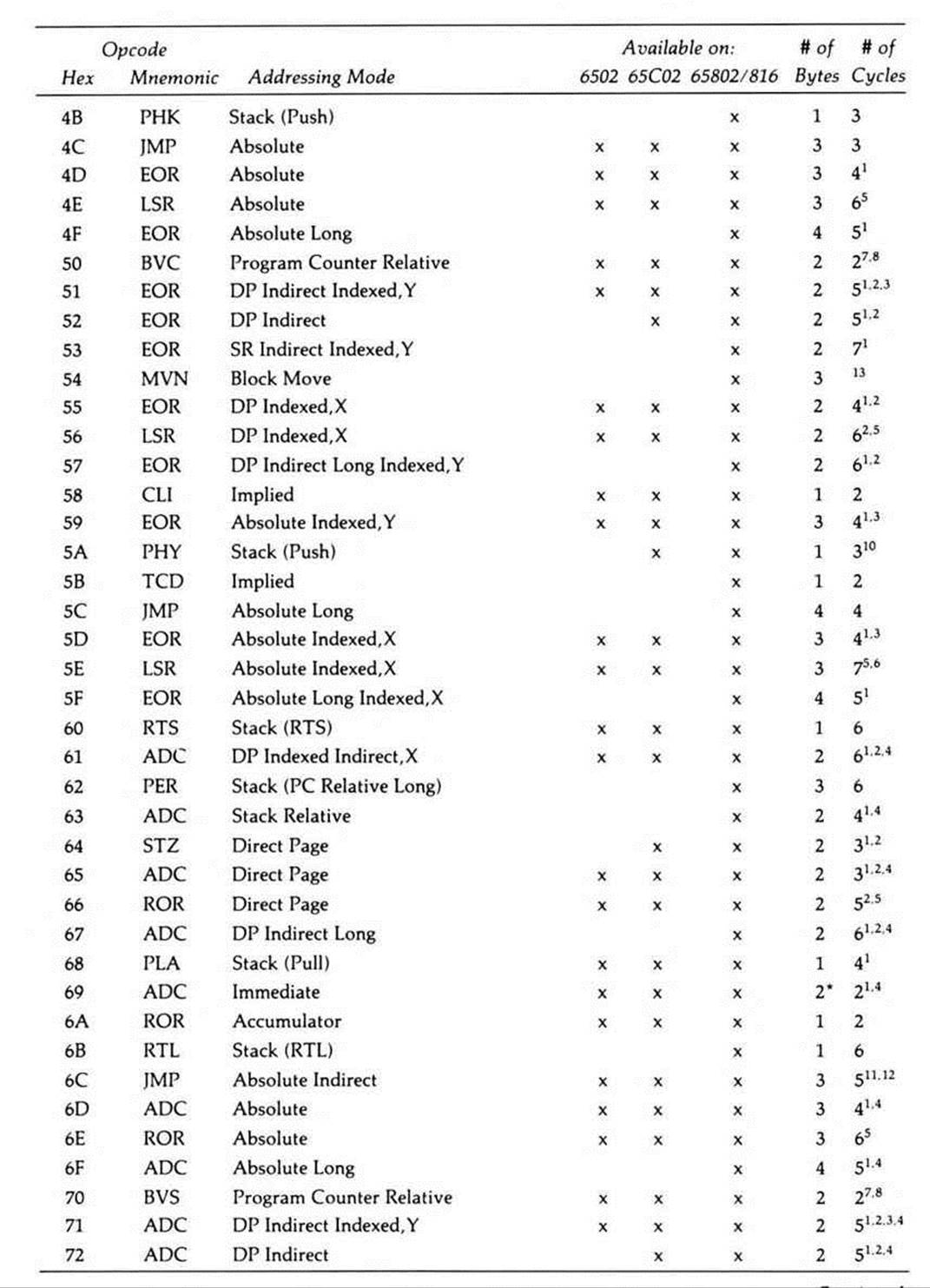

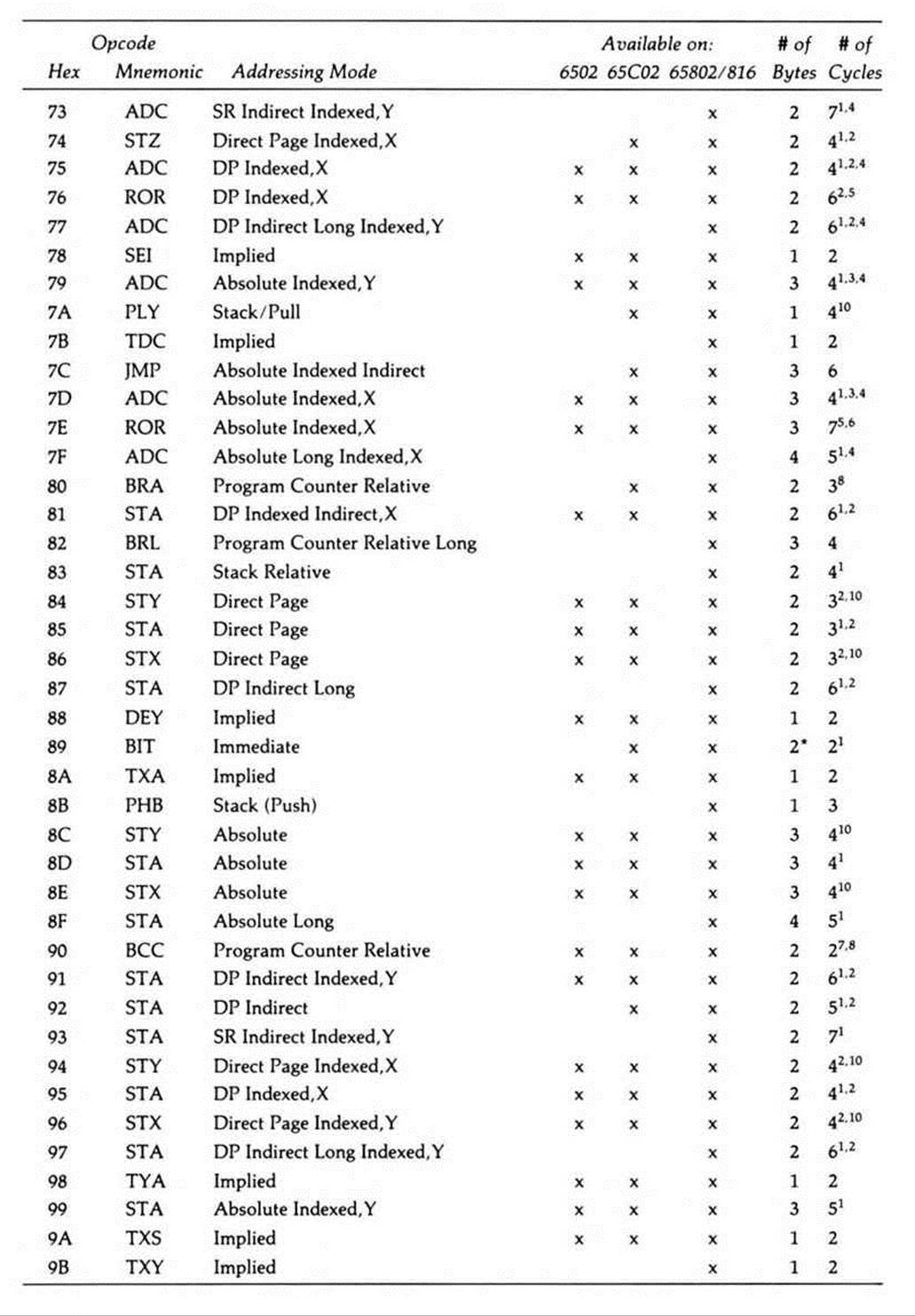

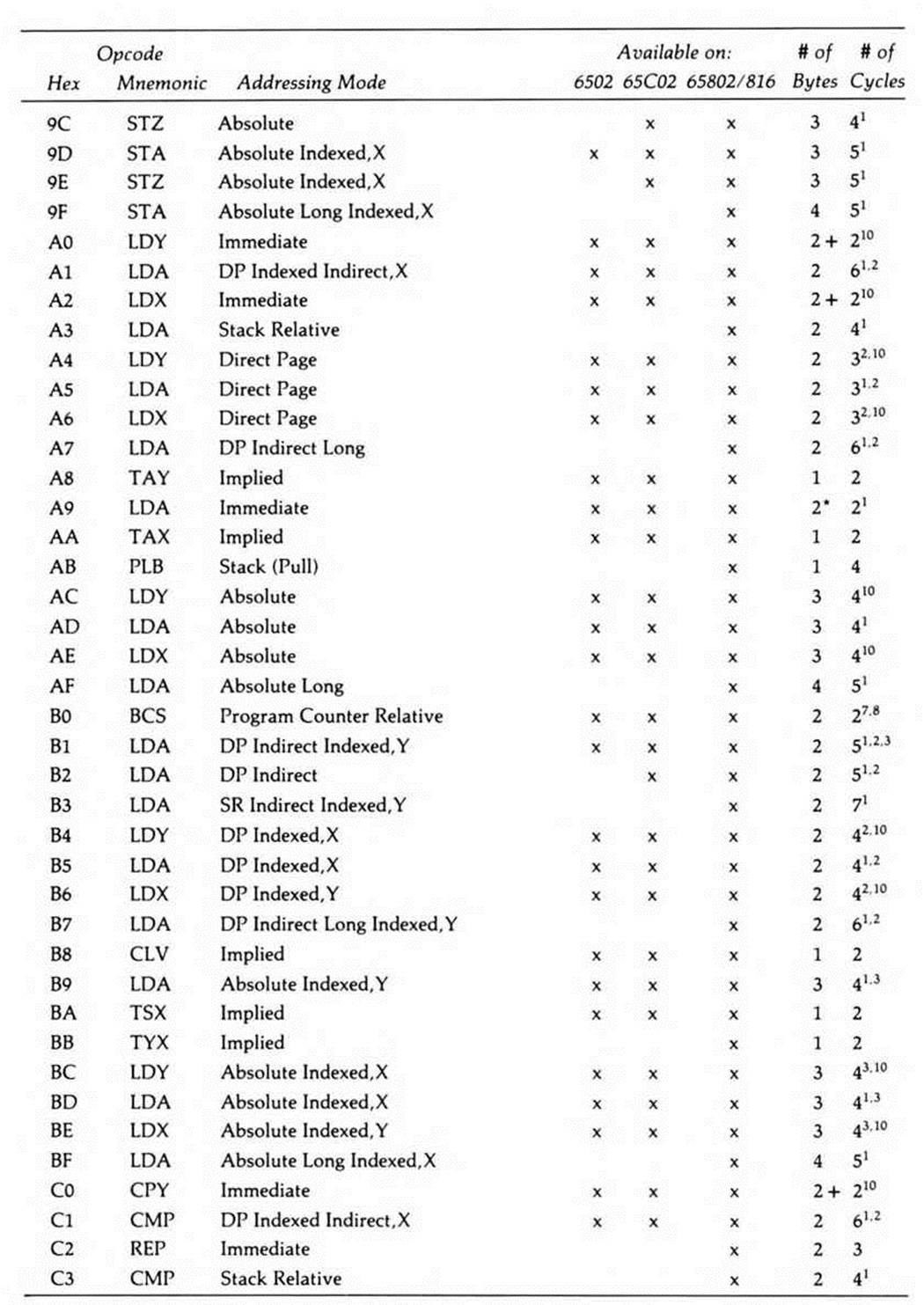

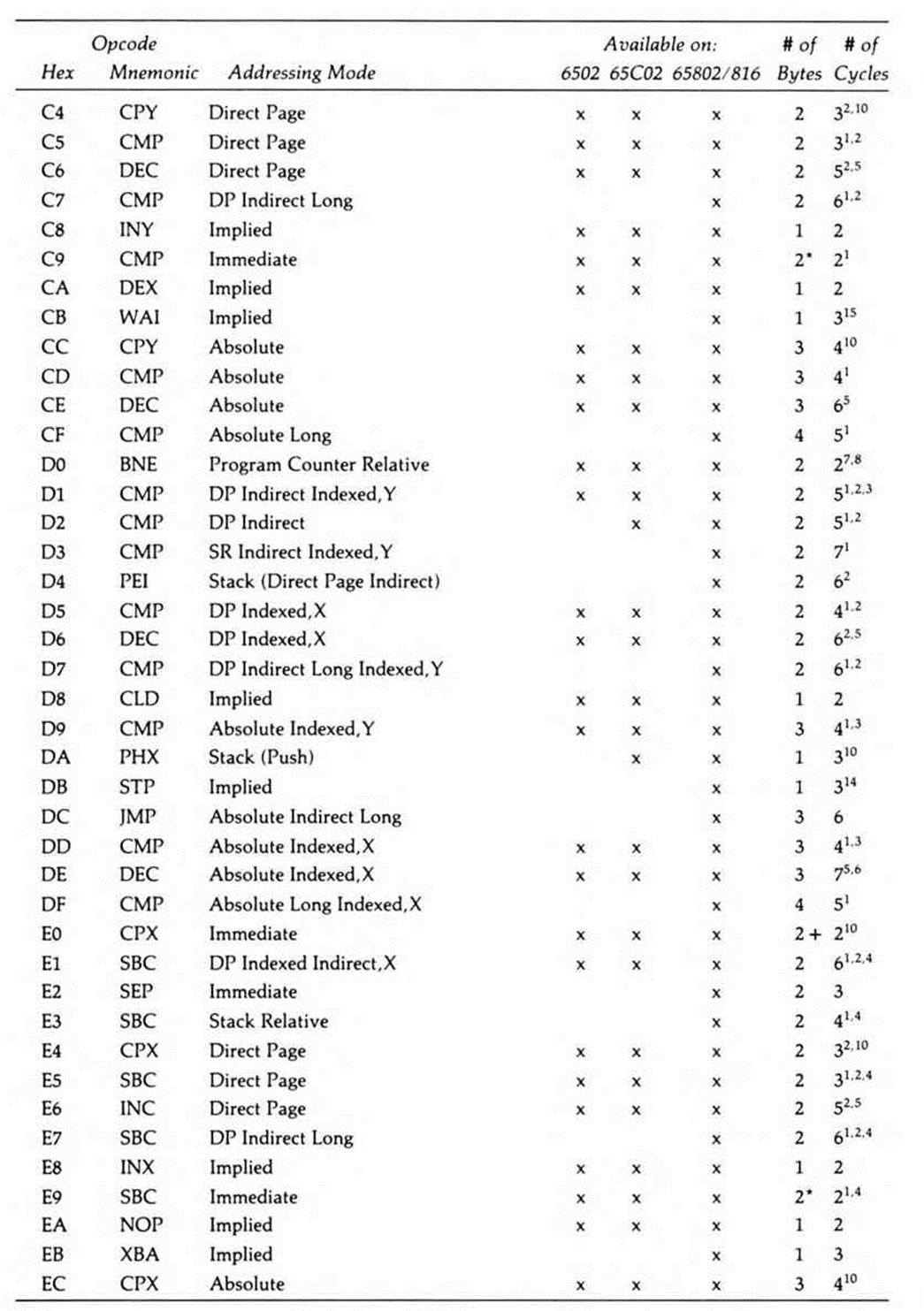

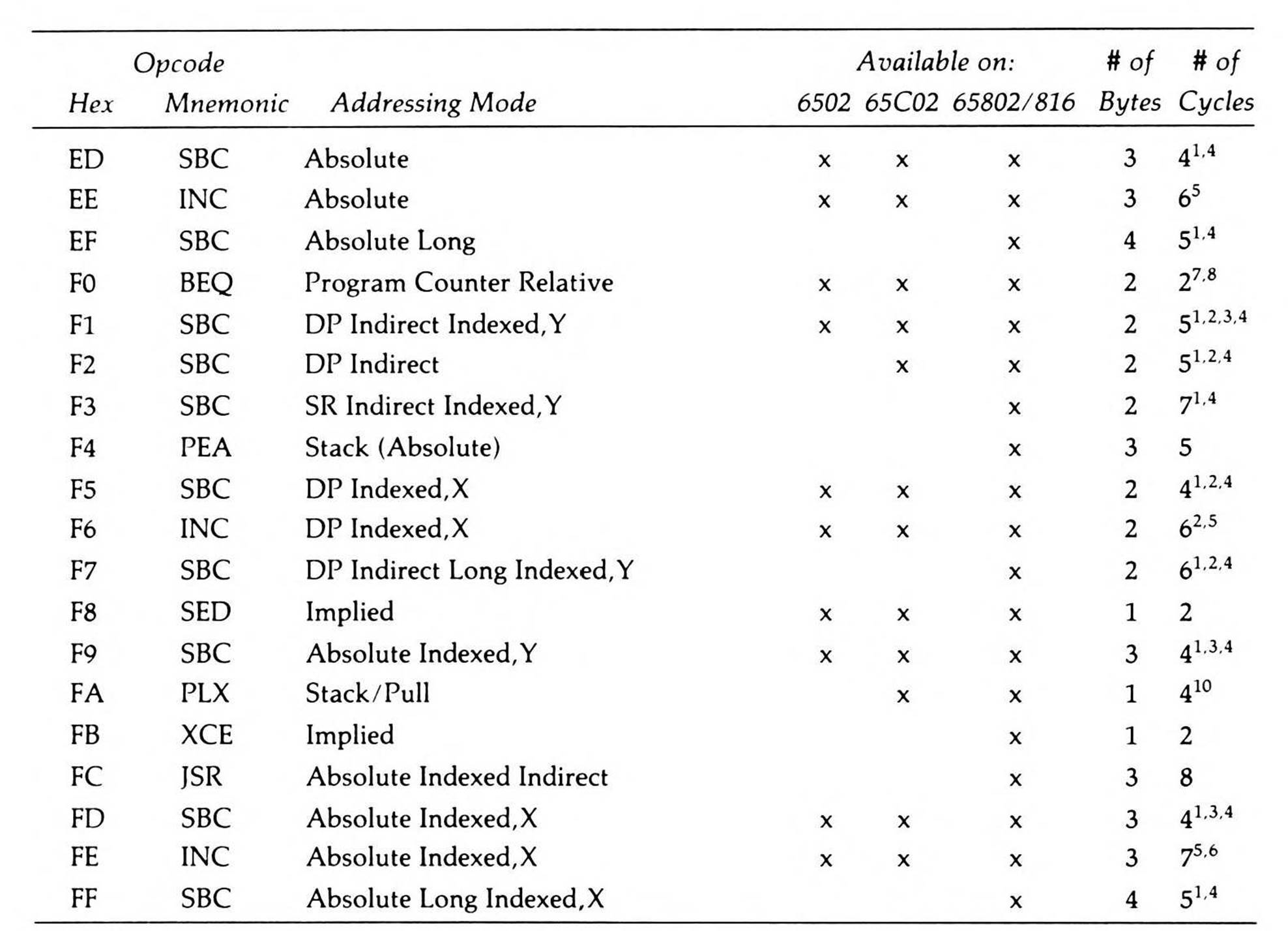

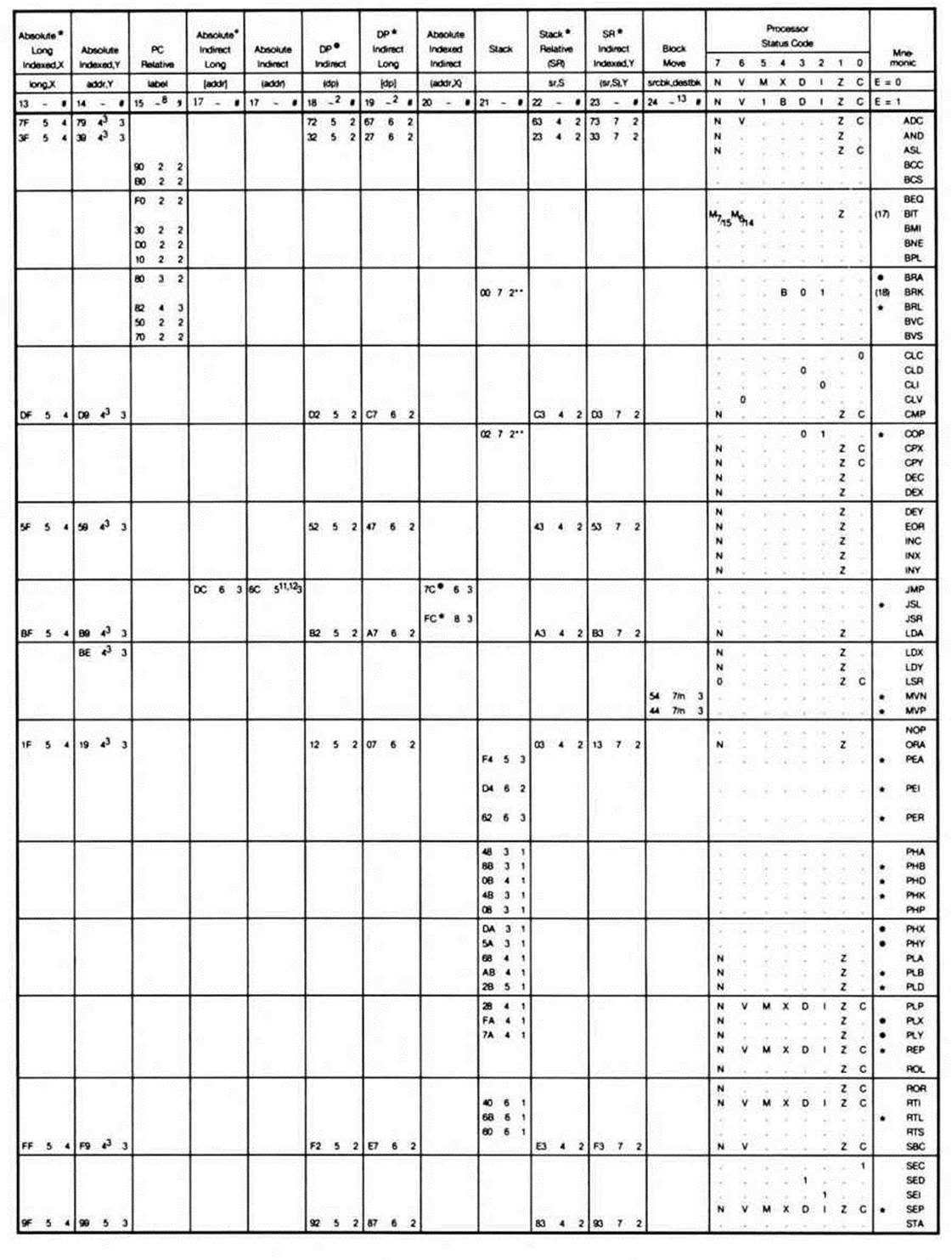

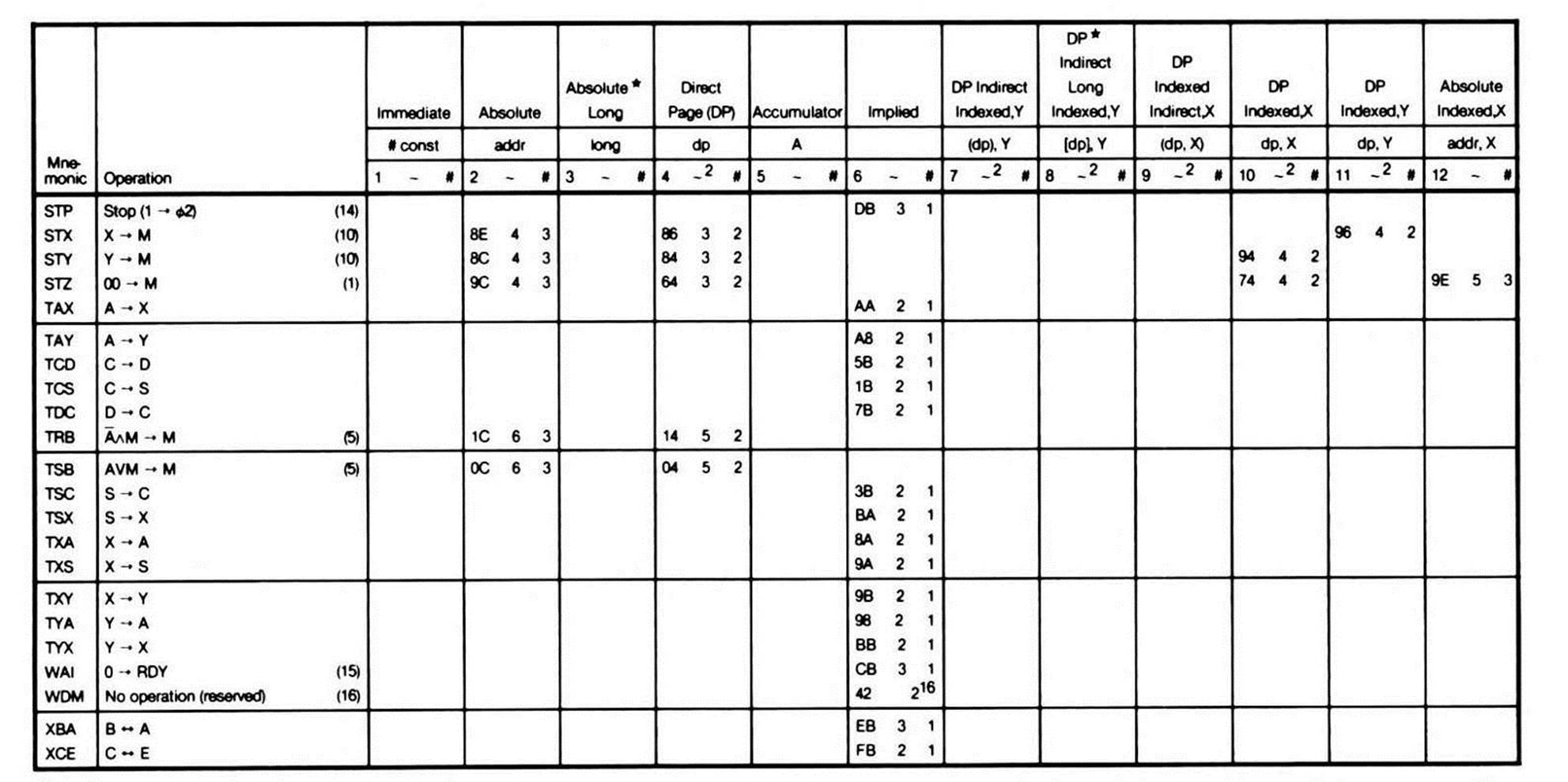

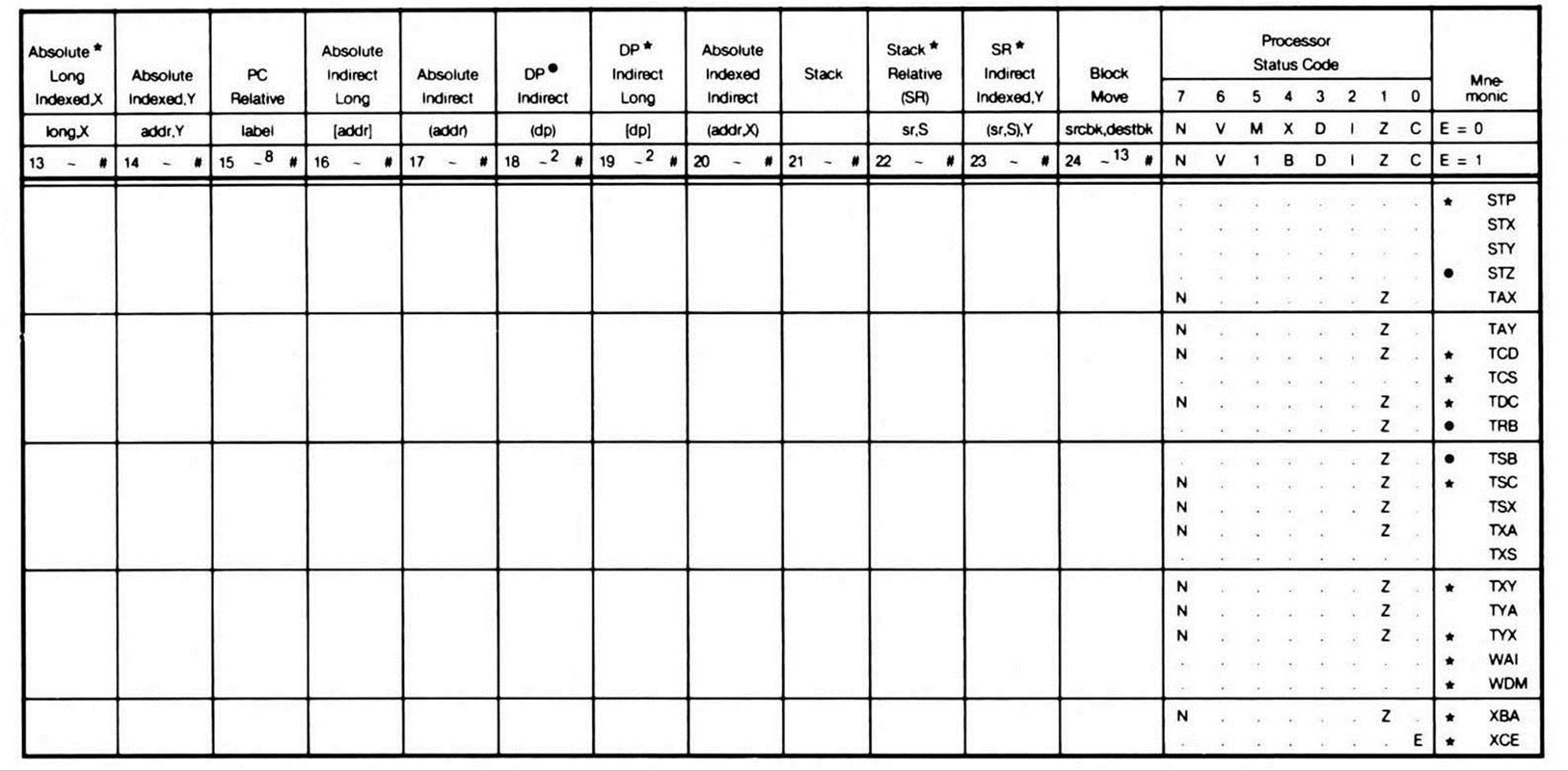

19. Instruction Lists

* Add 1 byte if m = 0 (16-bit memory/accumulator)

* * opcode is 1 byte, but program counter value pushed onto stack is incremented by 2 allowing for optional signature byte

+ Add 1 byte if x = 0 (16-bit index registers)

1 Add 1 cycle if m = 0 (16-bit memory/accumulafor)

2 Add 1 cycle if low byte of Direct Page register is other than zero (DL< >0)

3 Add 1 cycle if adding index crosses a page boundary

4 Add 1 cycle if 65C02 and d = 1 (decimal mode, 65C02)

5 Add 2 cycles if m = 0 (16-bit memory/accumulator)

6 Subtract 1 cycle if 65C02 and no page boundary crossed

7 Add 1 cycle if branch is taken

8 Add 1 more cycle if branch taken crosses page boundary on 6502, 65C02, or 65816/65802's 6502 emulation mode (e = 1)

9 Add 1 cycle for 65802/65816 native mode (e = 0)

10 Add 1 cycle if x = 0 (16-bit index registers)

11 Add 1 cycle if 65C02

12 6502: If low byte of operand is $FF ( i.e., operand is SxxFF): yields incorrect result

13 7 cycles per byte moved

14 Uses 3 cycles to shut the processor down; additional cycles are required by reset to restart it

15 Uses 3 cycles to shut the processor down; additional cycles are required by interrupt to restart it

10 Byte and cycle counts subject to change in future processors which expand WDM into 2-byte opcode portions of instructions of varying lengths

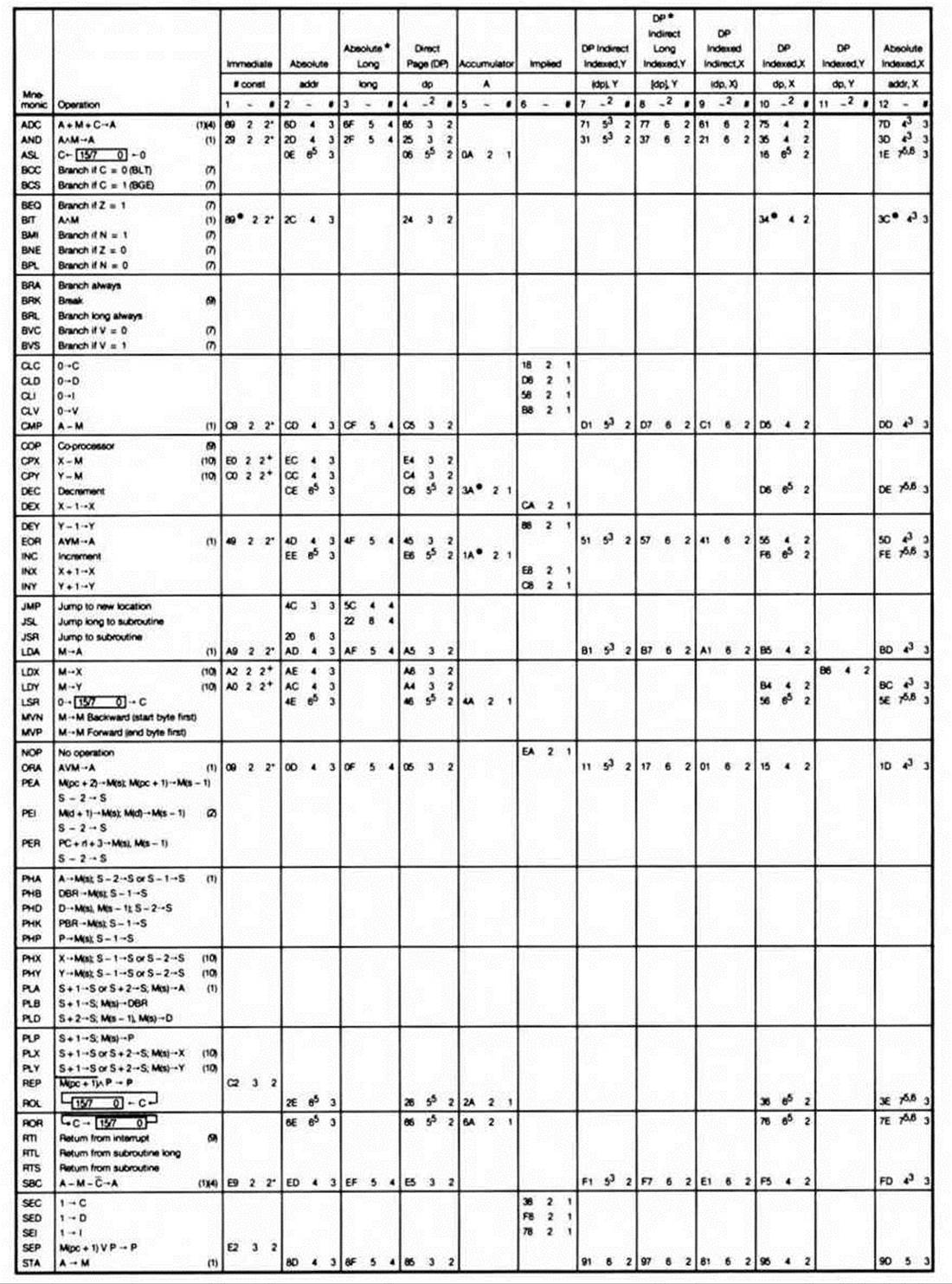

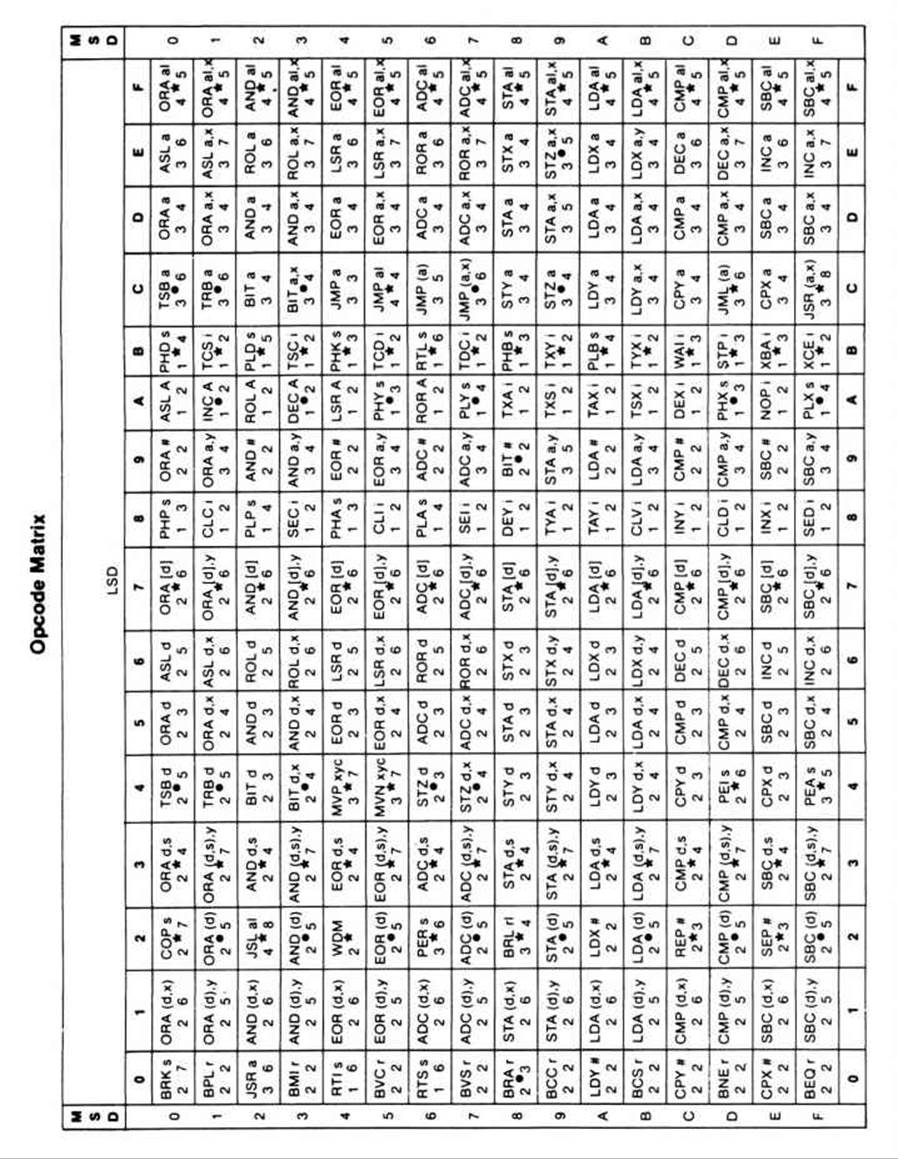

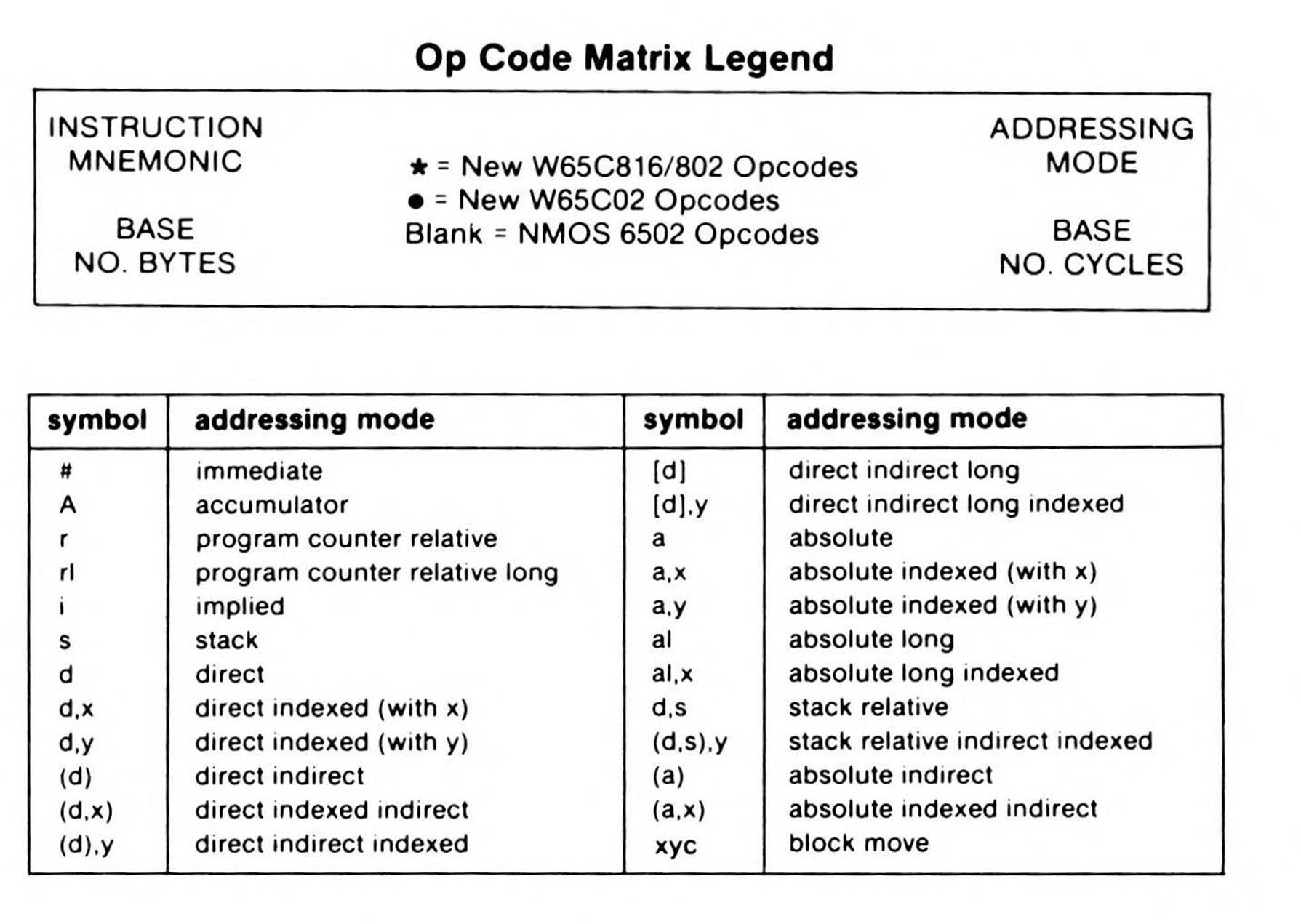

Opcodes Reference Chart

Processor

* Opcode or instruction first introduced on the 65C02

* Opcode or instruction first introduced on the 65816/65802 (not marked: first introduced on the NMOS 6502)

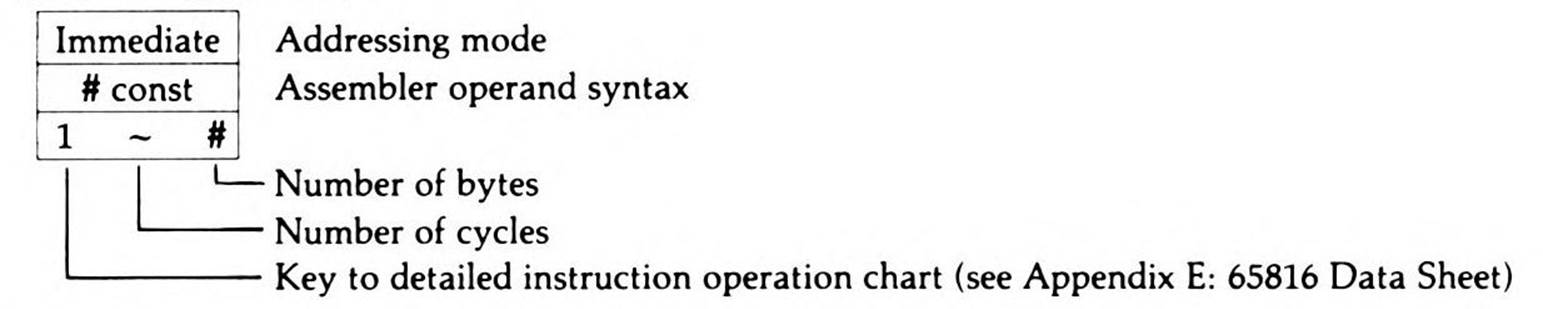

Addressing mode box:

Operation column:

|

A |

Accumulator |

|

X |

Index register X |

|

Y |

Index register Y |

|

M |

Contents of memory location specified by effective address |

|

M(d) |

Contents of direct page memory location pointed to by operand |

|

M(s) |

Contents of memory location pointed to by stack pointer |

|

M(pc) |

Current opcode pointed to by the program counter |

|

PC |

Memory location of current opcode pointed to by the program counter |

|

rl |

Two-byte operand of relative long addressing mode instruction |

|

+ |

Add |

|

— |

Subtract |

|

∧ |

And |

|

Or |

|

|

∨ |

Exclusive Or |

|

— |

Logical complement of a value or status bit (A indicates the complement of the value in the accumulator) |

|

Φ2 |

Phase 2 clock (hardware signal) |

|

RDY |

Ready (hardware signal) |

Bytes, cycles, and status codes:

* Add 1 byte if M = 0 (16-bit memory accumulator)

** opcode is 1 byte, but program counter value pushed onto stack is incremented by 2 allowing for optional signature byte

+ Add 1 byte if x = 0 (16-bit index registers)

n number of bytes moved

1 Add 1 cycle if m = 0 (16-bit memory accumulator)

2 Add 1 cycle if low byte of Direct Page register is other than zero (D L <> 0)

3 Add 1 cycle if adding index crosses a page boundary

4 Add 1 cycle if 65C02 and d = 1 (decimal mode, 65C02)

5 Add 2 cycles if m = 0 (16-bit memory/accumulator)

6 Subtract 1 cycle if 65C02 and no page boundary crossed

7 Add 1 cycle if branch is taken

8 Add 1 more cycle if branch taken crosses page boundary on 6502, 65C02, or 65816/65802's 6502 emulation mode (e= 1)

9 Add 1 cycle for 65802 65816 native mode (e= 0)

10 Add 1 cycle if x = 0 (16-bit index registers)

11 Add 1 cycle if 65C02

12 6502: If low byte of addr is $FF (i.e., addr is $xxFF): yields incorrect result

13 7 cycles per byte moved

14 Uses 3 cycles to shut the processor down; additional cycles are required by reset to restart it

15 Uses 3 cycles to shut the processor down; additional cycles are required by interrupt to restart it

16 Byte and cycle counts subject to change in future processors which expand WDM into 2-byte opcode portions of instructions of varying lengths

17 BIT: immediate n and v flags not affected; if m = 0, m(15) —»n and M(14) —>v; if m = 1, M(7) —>n and M(6) —*v

18 BRK: if b = 1 in pushed status register (6502, 65C02 and emulation mode e = 1), then interrupt was caused by

software BRK;

if 6502, d is unaffected by BRK; if 65C02 or 65816/65802, d is 0 after BRK

All materials on the site are licensed Creative Commons Attribution-Sharealike 3.0 Unported CC BY-SA 3.0 & GNU Free Documentation License (GFDL)

If you are the copyright holder of any material contained on our site and intend to remove it, please contact our site administrator for approval.

© 2016-2026 All site design rights belong to S.Y.A.